#### 1. General Information

CD / EIA-530 converter box allows to connect any equipment with Conditioned Diphase ("Manchester") interface to any equipment with RS-422/EIA-530 or EIA-530A interface.

CD - RS-422/EIA-530 converter specification.

- 1. Binary throughput: 16 / 32 /64 / 128 kbps

- 2. Generated clock frequencies (signal "114"): 16, 32, 64, 128 kHz ±25ppm

- 3. EIA-530/RS-422 interface:

- o RS-422/V.11/X.27 electrical parameters

- o D-SUB 25 female-type connector

- o DCE (modem) interface conformant to EIA-530 or EIA-530A standard

- o Control signals (DTR, RTS) are ignored by the converter.

#### 4. CD interface

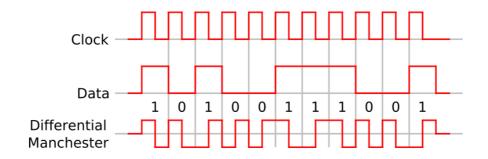

- o Conditioned Diphase "Manchester code"

- o Transmitter output: 2-wire balanced with transformer isolation

- o Transmitter output level: 3Vpp/5Vpp on 600Ω load,

- $\circ$  Transmitter output impedance:  $600\Omega$

- o Receiver input: 2-wire balanced with transformer isolation

- o Receiver sensitivity: < 0.3Vpp

- $\circ$  Receiver input impedance: 600 Ω

- o Interface socket: MC 1,5/4-G-3,81 (man. Phoenix Contact)

- 5. Power supply (options):

- 1. DC +12V..+30, < 2W, non-isolated, '-' connected to board's earth and GND line of RS-422 interface, PSU socket 5.5/2.5mm

- 2. AC 85...264VAC, 47...63Hz, <5W, IEC60320-C14 socket

- 6. Dimensions: 105 (130 with mounting flanges) mm 164mm 44mm

### 2. Front panel layout

Front panel contains:

- CD interface (MC 1,5/4-G-3,81 socket)

- RS-422/EIA-530 (DSUB-25) interface

- 'Power' status indicator (LED)

- 'CD' received signal status indicator for CD interface (LED)

- Received 'DATA' and 'CLK' signals indicators (LEDs) for RS-422/EIA-530 interfaces

#### 3. Connectors layout

1. **CD interface**, MC 1,5/4-G-3,81

| Pin | Signal Name            | Direction             |

|-----|------------------------|-----------------------|

| 1   | Transmit Signal Wire A | Output from converter |

| 2   | Transmit Signal Wire B |                       |

| 3   | Receive Signal Wire A  | Input to converter    |

| 4   | Receive Signal Wire B  |                       |

Pins are numbered from left to right.

### 2. Interface EIA-530 connector DSUB-25, female

| No | Pin                       | Code               | Cat. | Direction | Name (V.24 ITU circuit)                       | Type in DCE              | U |

|----|---------------------------|--------------------|------|-----------|-----------------------------------------------|--------------------------|---|

| 1  | 1                         | Shield             |      |           | Connected in DTE, not connected in DCE        |                          |   |

| 2  | A 2<br>B 14               | BA<br>TxD          | I    | to DCE    | TXD, Transmit Data (103)                      | Receiver                 | * |

| 3  | A 3<br>B 16               | BB<br><b>RxD</b>   | I    | from DCE  | RXD, Receive Data (104)                       | Transmitter              | * |

| 4  | A 4<br>B 19               | CA/CJ<br>RTS       | I    | to DCE    | Request To Send (105)/<br>Ready For Receiving | Receiver                 | * |

| 5  | A 5<br>B 13               | CB<br>CTS          | I    | from DCE  | Clear to Send (106)                           | Transmitter <sup>1</sup> | * |

| 6  | A 6<br>B 22 <sup>4</sup>  | CC<br>DSR          | I    | from DCE  | DCE ready DSR(107)<br>Data Set Ready          | Transmitter <sup>2</sup> | * |

| 7  | 7                         | AB<br>GND          |      |           | GND (102)                                     |                          | * |

| 8  | A 8<br>B 10               | CF<br><b>RLSD</b>  | I    | from DCE  | Received Line Signal<br>Detector (109)        | Transmitter              | * |

| 9  | A 17<br>B 9               | DD<br><b>RxClk</b> | I    | from DCE  | Receive Signal Timing (115)                   | Transmitter              | * |

| 10 | A 24<br>B 11              | DA<br>iTxClk       | I    | to DCE    | Transmit Signal Timing (113)                  | Receiver                 | * |

| 11 | A 15<br>B 12              | DB<br>oTxClk       | I    | from DCE  | Transmit Signal Timing (114)                  | Transmitter              | * |

| 12 | A 18                      | LL                 | II   | from DCE  | Local Loopback (141)                          | Receiver V.10            |   |

| 13 | A 20<br>B 23 <sup>5</sup> | CD<br><b>DTR</b>   | I    | from DCE  | DTE Ready (108)<br>Data Terminal Ready        | Receiver                 | * |

| 14 | A 21                      | RL                 | II   | from DCE  | Remote Lopback (142)                          | Receiver V.10            |   |

| 16 | A 25                      | TM                 | II   | from DCE  | Test Mode                                     | Receiver V.10            |   |

<sup>\* -</sup> used in CD/RS-422 converter

Transmitter<sup>1</sup>: CTS is connected directly to RTS or it is in constant ON state depending on CTS-A and CTS-B jumpers' state.

Transmitter<sup>2</sup>: DSR is connected directly to DTR or it is in constant ON state depending on DSR-A and DSR-B jumpers' state.

Pin 22<sup>4</sup> (CC/DSR – B) is used in EIA-530A as CE/RI (ring indicator).

Pin 23<sup>5</sup> (CD/DTR – B) is used in EIA-530A as GND.

#### 3. Power

#### 1. DC option

Converter box is powered by +9..+30VDC. The equipment is resistant to incorrect power connection, if the voltage is below 35V.

#### 2. AC option

Converter box is powered by 85...264VAC, 47...440Hz, connector IEC60320-C14

### 4. Signal definition – Conditioned Diphase (Manchester)

#### 5. Signal definition – RS-422/EIA-530

| Voltage V <sub>a</sub> -V <sub>b</sub> | Data bit | Control state |

|----------------------------------------|----------|---------------|

| >+0.3 V                                | 0        | ON            |

| < - 0.3 V                              | 1        | OFF           |

Clock signal definition: The condition of this circuit shall be ON and OFF for nominally equal periods of time and a transition from ON to OFF condition shall nominally indicate the centre of each signal element on data circuit.

### 4. Configuration

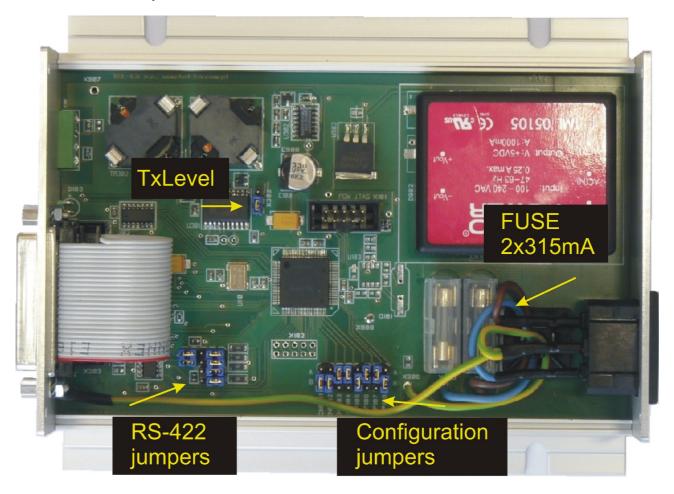

1. Board layout

## 2. Opening the housing

- 1. Plug off power supply cable

- 2. Unscrew four upper screw holding top and rear panel

- 3. Pull out the top shell

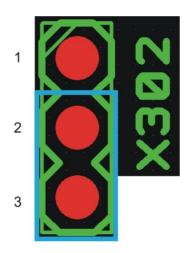

# 3. Setting the transmitter output level

| X302 | Output level |

|------|--------------|

| 1-2  | 5Vpp         |

| 2-3  | 3Vpp         |

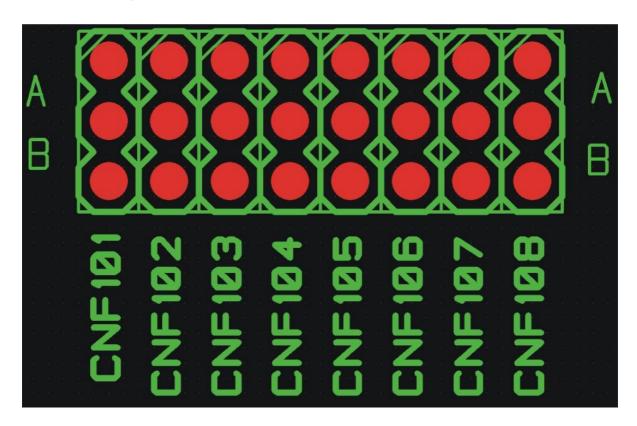

# 4. Configuration

# 1. CNF 101 – data signals' polarity on RS-422 interface

| CNF 101 | Polarity of data signals on RS-422 |

|---------|------------------------------------|

| A (vcc) | Inverse of data                    |

| B (gnd) | Normal polarity                    |

#### 2. CNF 102 – clock signals' polarity on RS-422 interface

| CNF 102 | Polarity of clock signals on RS-422 |

|---------|-------------------------------------|

| A (vcc) | Inverse of clock                    |

| B (gnd) | Normal polarity                     |

#### 3. CNF 104 – source of transmitter's clock

| CNF 104 | Source of transmitter's clock       |

|---------|-------------------------------------|

| A (vcc) | External "113" (EIA-530 pins 24,11) |

| B (gnd) | Internal "114" (EIA-530 pins 15,12) |

### 4. CNF 103, CNF 106 – PLL options

| CNF 103 | CNF 106 | Description                    |

|---------|---------|--------------------------------|

| B (gnd) | any     | PLL is disabled                |

| A (vcc) | A (vcc) | The bandwidth of PLL is wide   |

| A (vcc) | B (gnd) | The bandwidth of PLL is narrow |

#### Remarks:

- 1. PLL's occurs in both directions

- 2. If PLL is disabled, correct CD signal cannot be transmitted without a proper input clock.

- 3. If PLL is enabled and bandwidth is set to 'wide', time required to reach steady state is few seconds (eg. 15s by frequency jump of 10Hz)

- 4. If PLL is enabled and bandwidth is set to '*narrow*' time required to reach steady state is a several tens of second (eg. 50s by frequency jump of 10Hz)

## 5. CNF 105 - loops

| CNF 105 | Loop                                                                                                                                       |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------|

| A (vcc) | Data stream from RS-422 is returned to RS-422 interface and data stream received from CD interface is returned to CD interface transmitter |

| B (gnd) | Normal operation                                                                                                                           |

## 6. CNF 107, CNF 108 – throughput selection

| CNF 108 | CNF 107 | Throughput |

|---------|---------|------------|

| B (gnd) | B (gnd) | 16 kbps    |

| B (gnd) | A (vcc) | 32 kbps    |

| A (vcc) | B (gnd) | 64 kbps    |

| A (vcc) | A (vcc) | 128 kbps   |

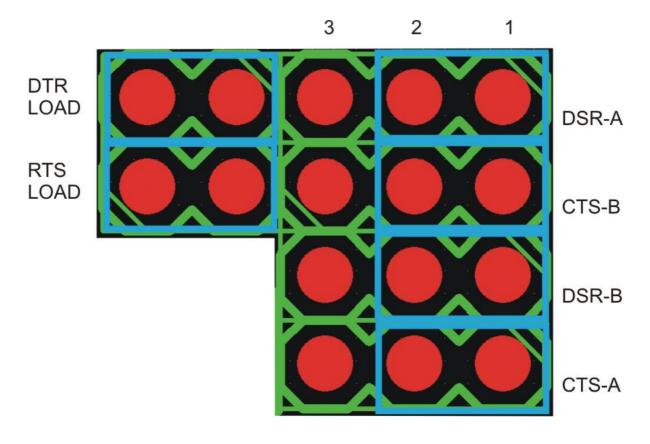

# 5. RS-422 jumpers layout and default configuration

## 6. RTS load configuration

| RTS LOAD jumper | RTS load              |

|-----------------|-----------------------|

| short           | resistive $100\Omega$ |

| open            | without load          |

### 7. CTS source configuration (X3/X4)

| CTS-A/B jumpers | CTS source |

|-----------------|------------|

| 1-2             | Always ON  |

| 2-3             | RTS        |

## 8. DTR load configuration (EIA-530)

| DTR LOAD jumper | DTR load              |

|-----------------|-----------------------|

| short           | resistive $100\Omega$ |

| open            | without load          |

## 9. DSR source configuration (EIA-530)

| DSR-A/B jumpers | DSR source |

|-----------------|------------|

| 1 - 2           | Always ON  |

| 2-3             | DTR        |

Fixed settings for the EIA-530A interface:

DSR-B - always 1-2 DTR LOAD - always open